## Scalable arrays of rf Paul traps in degenerate Si

J. Britton, <sup>1,a)</sup> D. Leibfried, <sup>2</sup> J. A. Beall, <sup>1</sup> R. B. Blakestad, <sup>2</sup> J. H. Wesenberg, <sup>3</sup> and D. J. Wineland <sup>2</sup>

(Received 11 August 2009; accepted 22 September 2009; published online 26 October 2009)

We report techniques for the fabrication of multizone linear radio frequency Paul traps that exploit the machinability and electrical conductivity of degenerate silicon. The approach was tested by trapping and laser cooling  $^{24}\text{Mg}^+$  ions in the two following trap geometries: a single-zone two-layer trap and a multizone surface-electrode trap. From the measured ion motional heating rate we determine an electric field spectral density at the ion's position of approximately  $1\times10^{-10}~(\text{V/m})^2\cdot\text{Hz}^{-1}$  at  $\omega_z/2\pi=1.125~\text{MHz}$  when the ion lies 40  $\,\mu\text{m}$  above the trap surface. One application of these devices is controlled manipulation of atomic ion qubits, the basis of one form of quantum information processing. [doi:10.1063/1.3254188]

Much recent ion trap research is motivated by the goal of building a useful quantum information processor (QIP) using trapped atomic ions as qubits (two-level quantum systems). In one approach, chains of laser-cooled ions are confined in linear radio frequency (rf) Paul traps with segmented trap electrodes. <sup>1-4</sup> Although the theoretical and experimental groundwork has been laid for a large-scale processor, so far only simple traps utilizing up to eight ions have been demonstrated. <sup>2,3,5</sup> Useful qubit computations could be performed using segmented electrodes which define an array of interconnected traps capable of holding and manipulating a large number of ions. <sup>1</sup>

Building such devices poses several microfabrication challenges. For example, the rf potentials (typically 100 to 500 V,  $\Omega_{RF}/2\pi=10$  to 100 MHz) needed for trapping suggest use of a low-loss substrate such as sapphire to prevent heating. However, such materials are incompatible with many through-wafer via technologies needed to distribute potentials to hundreds of control electrodes. Also, in vacuum, exposed dielectrics (e.g., the substrate) can accumulate charge giving rise to unwanted stray fields at the ions' location. High aspect-ratio electrodes can mitigate this problem but are difficult to fabricate for our target electrode width of  $\sim 10~\mu m$ . It is desirable that the ratio of electrode height to interelectrode distance ratio be greater than two.

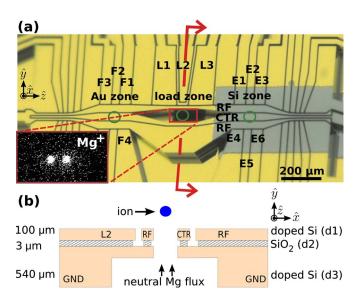

We used degenerate silicon as an electrode material and deep reactive ion etching to build structures that meet these objectives (Figs. 1 and 2). The Si was doped so that the number of electrons in its conduction band approaches that of a metal. In one device (Fig. 2) ions were trapped above the surface of a photolithographically patterned silicon-on-insulator (SOI) heterostructure. Compared with manually assembled traps, this approach reduces alignment errors. <sup>8,9</sup>

The devices were characterized by use of trapped and laser-cooled atomic <sup>24</sup>Mg<sup>+</sup> ions. We measured the rate at which ions gain kinetic energy from noisy ambient electric fields, an important characteristic for QIP.<sup>3,10</sup> Also, we obtain reasonable agreement between simulation of the trap poten-

The suitability of degenerate silicon as a trap electrode material was demonstrated by building and testing multiple ion traps. Two of these traps are discussed in this letter; see also Britton *et al.*<sup>11,12</sup>

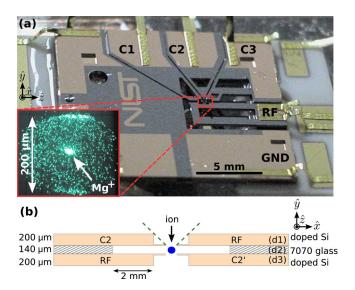

Figure 1 shows a single-zone two-layer anodically bonded trap that used a 7070 borosilicate glass as a dielectric spacer (0.06 loss tangent at 1 MHz). The device was built to demonstrate trapping using semiconducting trap electrodes; prior traps at NIST with similar a geometry used metal electrodes. The silicon was doped by the manufacturer with boron to give it a resistivity of  $0.5-1 \times 10^{-3} \ \Omega \cdot \text{cm}$ . After the trap electrode pattern was etched,

FIG. 1. (Color online) (a) Photograph of a two-layer silicon ion trap with a single trapping zone. The structure consists of two layers of silicon anodically bonded via a glass spacer. Inset: Fluorescence from a single laser-cooled  $^{24}\mathrm{Mg^+}$  ion imaged onto a camera (viewed from above). (b) The chip geometry in cross-section near the trapping region (indicated by a dot); not to scale. The interelectrode spacing was  $\sim\!6~\mu\mathrm{m}$  (e.g., between  $C_1$  and  $C_2$  near the ion). The ion-electrode distance was  $\sim\!122~\mu\mathrm{m}$  (e.g., the closest distance between  $C_2$  and the ion). The primed electrodes are not visible in the photograph. The two-tiered etch of the silicon trap electrodes permits a large solid angle for efficient collection of ion fluorescence (dashed lines).

Quantum Electrical Metrology Division, NIST, Boulder, Colorado 80305, USA

<sup>&</sup>lt;sup>2</sup>Time and Frequency Division, NIST, Boulder, Colorado 80305, USA

<sup>&</sup>lt;sup>3</sup>Department of Materials, University of Oxford, Oxford OX1 3PH, United Kingdom

tials and experimentally measured frequencies, important for reliable transport of ions between zones.<sup>2,9</sup>

a) Electronic mail: britton@nist.gov.

FIG. 2. (Color online) (a) Photograph of a multizone surface electrode ion trap fabricated from a single SOI wafer. Annotations highlight three trap zones (indicated by circles): a load zone (electrodes  $L_1-L_3$ ) and a pair of zones whose electrode surfaces were either bare silicon (electrodes  $E_1-E_6$ ) or 1  $\mu$ m evaporated gold ( $F_1-F_6$ , not all labels visible). Inset: Fluorescence from a pair of laser-cooled <sup>24</sup>Mg<sup>+</sup> ion imaged onto a charge coupled device camera (viewed from above). (b) Chip geometry in cross-section near the loading zone; not to scale. The interelectrode spacing was ~4  $\mu$ m (e.g., between  $E_1$  and  $E_2$ ). The SiO<sub>2</sub> was undercut about ~2  $\mu$ m by a wet etch. A hole cut in layer  $d_3$  permits passage of neutral <sup>24</sup>Mg from the back side of the wafer to the trap load zone without risk of shorting trap electrodes. The structural insulator (SiO<sub>2</sub>) was outside the field of view of the ions in all zones.

the silicon and glass wafers were diced into chips and bonded. In this first demonstration device, the chips were aligned by hand with the aid of a microscope. The electrodes near the ions were bare silicon; the nearest glass surface was more than 2 mm away from the trap zone.

The rf potential  $V_{\rm RF}$ =125 V at  $\Omega_{\rm RF}/2\pi$ =67 MHz, was applied with a  $\lambda/4$  resonant transformer with a loaded Q of 372. Typical ion lifetime with laser cooling was several hours; lifetime without laser cooling was up to 20 s. <sup>11</sup> The static trapping potentials were approximately  $V(C_1) = V(C_1') = V(C_3) = V(C_3') = 3$  V and  $V(C_2) = V(C_2') = 0$  V.

Figure 2 shows a trap with a surface-electrode geometry. The substrate was commercially available SOI with a Si resistivity of 5 to  $20\times10^{-3}~\Omega$  cm. The single-layer geometry is amenable to microfabrication, as all the trap electrodes lie in a single plane. The trap has 45 electrodes, permitting translation of ions from a loading zone to a pair of arms each with multiple trapping zones. Near the end of each arm the electrodes taper so that the ion-electrode distance drops from  $\sim$ 45 to 10  $\mu$ m; these zones were not employed for the results reported here.

Trapping conditions were  $V_{\rm RF}$ =50 V at  $\Omega_{\rm RF}/2\pi$ =67 MHz and the rf resonant transformer loaded Q was 90. Typical ion lifetime with Doppler cooling was around an hour; without cooling the lifetime was 10 s. Trap potentials were determined numerically and designed to null ion rf micromotion and properly orient the trap principle axes. Transport from the load zone to an experimental zone was repeated hundreds of times without ion loss (1 Hz repetition rate). The trap zone adjacent to electrodes  $E_2$  and  $E_5$  lies  $\sim$ 371  $\mu$ m away from the load zone and is  $\sim$ 41  $\mu$ m above the electrode surface. Typical static potentials were  $V(E_1)$

=0.71 V,  $V(E_2)$ =-0.58 V,  $V(E_3)$ =0.20 V,  $V(E_4)$ =0.20 V,  $V(E_5)$ =-1.81 V,  $V(E_6)$ =0.71 V, and  $V(E_{CTR})$ =0.11 V. For these potentials, the frequency along the  $\hat{z}$ -axis was measured to be  $\omega_z/2\pi$ =1.125 MHz, in agreement with simulation to within 4%. From simulation and measured radial frequencies  $(\omega_x/2\pi$ =7.80 MHz,  $\omega_y/2\pi$ =9.25 MHz), the rf potential was inferred. The trap depth predicted from simulation was 25 meV. Rf potentials as large as 150 V were applied to the devices; breakdown was not observed.

In the surface-electrode trap, kinetic energy gained by ions in the absence of cooling was measured by use of a Doppler recooling technique. <sup>15,16</sup> As a test of the effect of electrode material type on ion motional heating, the two following regions were created: one with gold-coated electrodes and one with bare silicon electrodes (Fig. 2). Heating measurements were made over each zone in a static potential well at an ion-electrode distance of ~40  $\mu$ m. We observed that ion motional heating in the absence of laser cooling <sup>10</sup> was the same in the gold and bare silicon experimental zones. The inferred electric field noise spectral density was competitive with other room temperature microtraps and was determined to be approximately  $1 \times 10^{-10} \ (V/m)^2 \cdot Hz^{-1}$  at  $\omega_z/2\pi=1.125 \ \text{MHz} \ (\sim 20 \times 10^3 \ \text{quanta/s})$ . <sup>2,10,15,17</sup> Because the rate of energy gain was about the same in both zones and somewhat variable from day to day, we suspect the heating was caused in part by noise injected from an unidentified external source.

The two following types of Si-insulator-Si heterostructures were used for these traps: anodically bonded Si-glass-Si and commercial SOI. In both, trap electrodes were electrically isolated islands of conducting silicon formed by selective removal of material (Bosch DRIE). The etch pattern was defined by  $\sim 7~\mu m$  photoresist. The narrowest practical channel width in a 200  $\mu m$  wafer was 4  $\mu m$  (50:1 aspect-ratio). Note that typical wet etch techniques for silicon (KOH, EDP) are ineffective in degenerate silicon. <sup>18</sup>

Two-tiered etching [Fig. 1(b)] was accomplished by use of a pair of overlapping etch masks and the additivity of the etch process. The lower mask was  $\sim 1~\mu m$  thermal oxide and the top was  $\sim 7~\mu m$  photoresist. After an initial deep etch, hydrogen fluoride (HF) was used to etch the exposed oxide, leaving the photoresist intact. A second deep etch completed the two-tier structure. <sup>12</sup>

Si-glass-Si heterostructures were assembled by use of anodic bonding. <sup>18</sup> In our experiments we fabricated structures with  $d_1$ =100 to 200  $\mu$ m,  $d_2$ =140 to 200  $\mu$ m, and  $d_3$ =100 to 600  $\mu$ m. Anodic bonding of full wafers and individual chips was performed on a hotplate (450 °C and 500 V). Prior to bonding, chips were cleaned with HF and Piranha etch.

Through-wafer features were etched in the glass spacers before anodic bonding by ultrasonic milling. Alternately, it may be possible to etch the glass after bonding by use of silicon as a mask for a glass etchant such as HF. For HF:H<sub>2</sub>O=1:10, the vertical etch rate is reported to be  $10 \ \mu \text{m/h}$  with an undercut of 15  $\ \mu \text{m/h}$ .

Commercial SOI wafers are available with  $d_1$ =0.1 to 500  $\mu$ m,  $d_2$ =0.1 to 10  $\mu$ m,  $d_3$ =100 to 500  $\mu$ m, and a resistivity as low as  $0.5 \times 10^{-3}$   $\Omega \cdot \text{cm}$ , which helps reduce rf loss. For SOI, thermal silicon oxide usually forms the insulating layer  $(d_2)$ .

Ion trap chips were packaged in either co-fired ceramic chip carriers or planar ceramic circuit boards, both high vacuum compatible ( $\sim 1 \times 10^{-9}$  Pa) and with gold traces. The chips were adhered to the chip carriers by a ceramic paste. Ohmic contacts were deposited on the silicon chip (10 nm Al, 10 nm Ti, and 1000 nm Au). Native oxide was stripped by a plasma etch or HF dip before deposition of ohmic contacts and again immediately before inserting a finished chip into the trap vacuum system.

The <sup>24</sup>Mg<sup>+</sup> ions were created by electron bombardment or resonant photoionization of thermally evaporated neutral magnesium atoms. The atom source was isotopically enriched <sup>24</sup>Mg packed inside a resistively heated stainless tube with an aperture pointing toward the trap loading zones. The ions were cooled to the Doppler limit by use of a laser tuned below the <sup>24</sup>Mg<sup>+</sup> D2 transition at 280 nm. <sup>12,15</sup>

This letter presents approaches to building ion trap arrays that use degenerate silicon as an electrode material. Characteristics of two trap structures were presented and their performance suggests that this technology is compatible with trapping large arrays of ions for applications in QIP. The planar surface-electrode device demonstrated the feasibility of building monolithic ion traps in SOI. In addition to multizone traps, the goal of quantum computing could potentially be advanced by integration of these types of devices with CMOS electronics (e.g., via bump bonding), MEMS optics, and optical fibers.<sup>6</sup>

We thank J. Bollinger and J. Amini for comments on the manuscript. This work was supported by IARPA and the NIST Quantum Information Program. J.H.W. thanks the Danish Research Agency for financial support. This letter is a contribution of NIST and not subject to U.S. copyright.

- <sup>3</sup>R. Blatt and D. J. Wineland, Nature (London) **453**, 1008 (2008).

- <sup>4</sup>D. Hucul, M. Yeo, S. Olmschenk, C. Monroe, W. K. Hensinger, and J. Rabchuck, Quantum Inf. Comput. **8**, 0501 (2008).

- <sup>5</sup>H. Häffner, W. Hänsel, C. F. Roos, J. Benhelm, D. Chek-al-kar, M. Chwalla, T. Körber, U. D. Rapol, M. Riebe, P. O. Schmidt, C. Becher, O. Guhne, W. Dur, and R. Blatt, Nature (London) 438, 643 (2005).

- <sup>6</sup>J. Kim, S. Pau, Z. Ma, H. R. McLellan, J. V. Gates, A. Kornblit, R. E. Slusher, R. M. Jopson, I. Kang, and M. Dinu, Quantum Inf. Comput. 5, 515 (2005).

- <sup>7</sup>D. Kielpinski, Ph.D. thesis, University of Colorado, 2001.

- <sup>8</sup>M. A. Rowe, A. Ben-Kish, B. Demarco, D. Leibfried, V. Meyer, J. Beall, J. Britton, J. Hughes, W. M. Itano, B. Jelenkovic, C. Langer, T. Rosenband, and D. J. Wineland, Quantum Inf. Comput. 2, 257 (2002).

- <sup>9</sup>R. B. Blakestad, C. Ospelkaus, A. P. VanDevender, J. M. Amini, J. Britton, D. Leibfried, and D. J. Wineland, Phys. Rev. Lett. **102**, 153002 (2009).

- <sup>10</sup>Q. A. Turchette, D. Kielpinski, B. E. King, D. Leibfried, D. M. Meekhof, C. J. Myatt, M. A. Rowe, C. A. Sackett, C. S. Wood, W. M. Itano, C. Monroe, and D. J. Wineland, Phys. Rev. A 61, 063418 (2000).

- <sup>11</sup>J. Britton, D. Leibfried, J. Beall, R. B. Blakestad, J. Bollinger, J. Chiaverini, R. J. Epstein, J. D. Jost, D. Kielpinski, C. Langer, R. Ozeri, R. Reichle, S. Seidelin, N. Shiga, J. H. Wesenberg, and D. J. Wineland, arXiv:quant-ph/0605170v1 (unpublished).

- <sup>12</sup>J. Britton, Ph.D. thesis, University of Colorado, 2008.

- <sup>13</sup>J. Chiaverini, R. B. Blakestad, J. Britton, J. D. Jost, C. Langer, D. Leibfried, R. Ozeri, and D. J. Wineland, Quantum Inf. Comput. 5, 419 (2005).

- <sup>14</sup>S. Seidelin, J. Chiaverini, R. Reichle, J. J. Bollinger, D. Leibfried, J. Britton, J. H. Wesenberg, R. B. Blakestad, R. J. Epstein, D. B. Hume, W. M. Itano, D. J. Jost, C. Langer, R. Ozeri, N. Shiga, and D. J. Wineland, Phys. Rev. Lett. 96, 253003 (2006).

- <sup>15</sup>R. J. Epstein, S. Seidelin, D. Leibfried, J. H. Wesenberg, J. J. Bollinger, J. M. Amini, R. B. Blakestad, J. Britton, J. P. Home, W. M. Itano, J. D. Jost, E. Knill, C. Langer, R. Ozeri, N. Shiga, and D. J. Wineland, Phys. Rev. A 76, 033411 (2007).

- <sup>16</sup>J. H. Wesenberg, R. J. Epstein, D. Leibfried, R. B. Blakestad, J. Britton, J. P. Home, W. M. Itano, J. D. Jost, E. Knill, C. Langer, R. Ozeri, S. Seidelin, and D. J. Wineland, Phys. Rev. A 76, 053416 (2007).

- <sup>17</sup>L. Deslauriers, P. Haijan, P. Lee, K. Brickman, B. Blinov, M. Madsen, and C. Monroe, Phys. Rev. A 70, 043408 (2004).

- <sup>18</sup>Q. Tong and U. Gösele, Semiconductor Wafer Bonding: Science and Technology (Wiley, New York, 1999).

- <sup>19</sup>T. Corman, P. Enoksson, and G. Stemme, J. Micromech. Microeng. 8, 84 (1998).

- <sup>20</sup>D. L. Stick, Ph.D. thesis, The University of Michigan, 2007.

<sup>&</sup>lt;sup>1</sup>D. Kielpinski, C. Monroe, and D. J. Wineland, Nature (London) **417**, 709 (2002).

<sup>&</sup>lt;sup>2</sup>J. M. Amini, J. Britton, D. Leibfried, and D. J. Wineland, *Atom Chips*, edited by J. Reichel and V. Vuletic (Wiley-VCH, Weinheim, to be published), arXiv:0812.3907.